Laporan Akhir 1

1. Jurnal [Kembali]

Jurnal praktikumnya dapat dilihat pada gambar dibawah ini:

2. Hardware [Kembali]

Hardware yang digunakan pada saat praktikum adalah sebagai berikut:

a. Modul D'Lorenzo

Adalah modul yang digunakan saat praktikum dalam membantu merangkaian rangkaian sesuai dengan modul yang dipraktikumkan, modul ini terdiri dari panel - panel yakni:

1.Panel DL 2203D

2.Panel DL 2203C

3.Panel DL 2203S

Adalah kabel yang saling menghubungkan komponen - komponen pada modul

Gambar 4. Jumper

3. Rangkaian simulasi [Kembali]

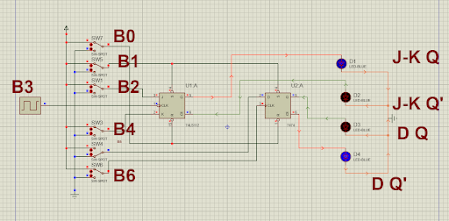

Untuk gambar rangkaian simulasi percobaan 1 dengan kondisi 5 adalah sebagai berikut:

Gambar rangkaian sebelum keadaan ON

Gambar 5. Rangkaian

4. Prinsip kerja [Kembali]

Dalam mempermudah mengamati prinsip kerja dari rangkaian ini maka dua buah output dari flip flop tersbebut dipisahkan dan diberi tanda masing - masing. Output dari J-K flip flop adalah J-K Q, J-K Q' dan untuk D flip flop adalah D Q dan D Q'. Pada Bagian J-K flip - flop bagian dari S dan R merupakan pin set dan resetnya, sementara Pin J dan K untuk mengaktifkan inputnya, sementara pin clock untuk mengatur banyak pulsa yang diberikan agar dapat berganti outputnya. J - K flip flop yang digunakan pada ini adalah flip - flop yang akan aktif jika signal clocknya berada pada bagian aktif low, berarti outputnya akan berganti jika clock berubah dari 1 ke 0.

Sesuai dengan kondisi yang diberikan, pin yang mengontrol input J dan K adalah switch B2 dan B3 yang dimana pada kondisi nilai kedua switch tersebut adalah 1. Sesuai dengan karakteristik dari J K flip flop sendiri, jika kedua input bernilai 1 maka outputnya akan berada pada kondisi toogle. Kondisi toogle ini berarti nilai outputnya akan terus berganti - ganti (misalnya pada saat sebelumnya output adalah 0), dan pin J K nya adalah 1, maka ketika clock berada di active low, maka output akan berganti dari 0 ke 1, proses ini akan terus berulang apabila kedua input pin J K adalah 1.

Selanjutnya pada flip flop D, prinsip kerja dari flip flop D iyalah output akan berubah mengikuti besaran inputnya misal pin D diberi nilai 1, maka output akan 1, begitu juga sebaliknya. Namun, kapan waktu berubah pada flip flop D ini dipegaruhi oleh clock yang diberikan, pada rangkaian percobaan ini flip flop D yang digunakan adalah flip flop D active HIGH yang berarti perubahan data output terjadi apabila clock berubah dari 0 ke 1.

5. Video

[Kembali]

Untuk video penjelasan praktikumnya dapat dilihat di bawah berikut:

6. Analisa [Kembali]

Soal analisa yang diberikan ada 3 yakni:

1. Bagaimana jika B0, dan B1 sama-sama diberi logika 0, apa yang terjadi pada rangakaian?

jawab:

Jika B0 dan B1 diberi logika 0, maka output dari flip-flop J-K akan menghasilkan output tak menentu (undetermined), hal ini dikarenakan pin yang terhubung pada B0 dan B1 adalah pin set dan reset, dan rangkaian yang digunakan adalah flip flop active LOW, ini berarti output akan berganti jika ada perubahan input clock dari 1 ke 0, dan apabila pin R S berubah dari 1 ke 0 secara bersamaan maka output akan berada pada kondisi HIGH, dan dapat menyebabkan kondisi tak menentu (undetermined condition).

2. Bagaimana jika B3 diputuskan/tidak dihubungkan pada rangkaian apa yang terjadi pada rangkaian!

jawab:

Switch B3 dihubungkan ke pin clock pada flip-flop, clock sendiri adalah komponen yang berfungsi untuk menentukan kapan terjadinya perpindahan data. Jadi, apabila clock diputuskan maka data output tidak akan mengalamai perubahan, meskipun input pada J-K flip flop diganti dari 1 dan 0 (atau sebaliknya).

Outputnya tidak akan berganti karena input clock yang berfungsi memberi tahu kapan data bisa berganti tidak terhubung ke rangkaian.

3. Jelaskan apa yang dimaksud dengan kondisi toogle, kondisi not change, dan kondisi terlarang pada flip flop!

jawab:

- Kondisi toogle adalah kondisi dimana outputnya selalu berganti nilai pada setiap pergantian kondisi clock aktif. Misal pada kondisi sebelumnya output dari clock adalah Q=0, maka pada kondisi selanjutnya nilai Q akan berubah dari 0, 1, 0, 1, 0, 1, dst setiap pergantian kondisi aktif clock. Berikut contoh dari output toogle ketika clock active HIGH.

Gambar 6. Output dari kondisi toogle

- Kondisi not change adalah kondisi pada flip-flop ketika nilai yang dikeluarkan oleh output tidak berganti, misal pada waktu t0 = adalah saat pergantian clock, misal output Q pada t0 adalah 0, kondisi not change menyatakan bahwa nilai output Q pada t1 juga bernilai 0, begitupun sebaliknya

- Kondisi terlarang adalah sebuah kondisi pada flip flop ketika nilai kedua output adalah sama (Q = Q'). Nilai ini secara prinsip aljabar boolean tidak diperbolehkan karena besar nilai Q harus berkebalikan dengan Q'. Nilai ini akan menyebabkan terjadinya ketidakpastian nilai output apabila kedua input diubah secara langsung secara bersamaan.

7. Link Download [Kembali]

Tidak ada komentar:

Posting Komentar