Modul 2 Flip Flop

DAFTAR ISI

Tujuan dari praktikum M2 ini adalah:

- Merangkain dan menguji berbagai macam flip-flop

2. Alat dan Bahan

[Kembali]

Peralatan yang digunakan pada modul 2 kali ini adalah:

a. Modul D'Lorenzo

Adalah sebuah modul yang berisi panel - panel gabungan yang masing-masing memiliki kegunaan tersendiri, panel-panel tersebut antara lain:

1. Panel DL 2203C

2. Panel DL 2203D

3. Panel DL 2203SS

Gambar dari modul tersebut sebagai berikut:

Gambar 1. Modul D'Lorenzo

b. Kabel jumper

Adalah penghubung yang berfungsi untuk menyambung bagian antar panel/rangkaian.

Gambar 2. Kabel jumper

3. Dasar Teori

[Kembali]

Teori yang akan digunakan pada praktikum M2 Kali ini adalah mengenai flip flop. Flip - flop adalah komponen elektronika yang memiliki dua buah kondisi stabil. Flip-flop biasanya digunakan sebagai bagian untuk menyimpan data dari hasil operasi logika (dengan kata lain menyimpan data dalam bentuk 1 atau 0). Flip flop mempuyai dua buah otuput yang salah satu outputnya adalah komplemen (kebalikan dari output satu lagi). Pada praktikum kali ini akan dibahas mengenai beberapa jenis flip -flop yakni S-R flip-flop, J-K flip-flop, D flip-flop, dan T flip-flop. Untuk penjebaran lengkapnya akan disampaikan pada bagian dibawah ini.

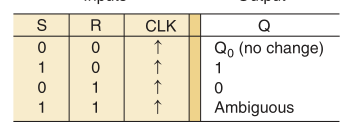

A. R-S flip flop

R-S flip flop adalah sebuah flip flop dasar dari semua flip flop yang memiliki dua buah input gerbang yakni R dan S. Gerbang R memiliki adalah pin yang berfungsi untuk meresetkan (mengembalikan) keadaan flip - flop menjadi keadaan semula (outputnya 0). Sementara pin S adalah pin "SET" yang berfungsi untuk menetapkan output dari flip flop menjadi 1. Berikut ini adalah rangkaian internal dari R-S flip flop.

Gambar 3. Rangkaian internal R-S flip flop

Dan untuk komponen dan tabel logika dari R-S flip flop adalah sebagai berikut:

Gambar 4. Simbol komponen S-R flip flop

Gambar 5. Tabel logika dari R-S flip flop

B. J-K flip flop

J-K flip flop adalah flip flop yang memiliki karakteristik yang mirip dengan R-S flip flop. Namun, J-K flip flop memiliki kelebihan dari jenis S-R flip flop yakni tidak adanya kondiis tak menentu, kondisi tak menentu tersebut digantikan dengan kondisi yang dinamakan kondisi toogle. Kondisi toogle adalah kondisi ketika setiap terjadinya perubahan clock aktif, maka output akan berubah berlawanan dengan output sebelumnya. Rangkaian internal dari J-K flip flop dapat dfilihat pada gambar berikut:

Gambar 6. Rangkaian inrtenal J-K flip flop

Sementara itu untuk simbol dari J-K flip flop beserta tabel logikanya adalah:

Gambar 7. Simbol dari J-K flip flop

Gambar 8. Tabel logika J-K flip flop

Dilihat dari tabel logika dari J-K flip flop memiliki kemiripan yang signifikan dengan tabel logika dari R-S flip-flop. Bedanya hanya terletak ketika besar nilai input J dan input K berada pada nilai 1 yang akan menghasilkan kondisi toogle (output berganti - ganti).

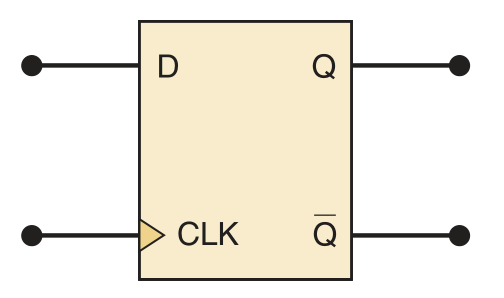

C. D flip-flop

D flip-flop adalah pengembangan dari S-R atau J-K flip flop. Maksud dari pengembangan ini adalah D flip flop merupakan flip -flop S-R (atau J-K) yang pada input K (atau R) ditambahkan sebuah inverter, kemudian titik input awal digabung sehingga menjadi satu pin input saja. Hal ini akan mengakibatkan besar dari nilai input D sama dengan nilai output Q sesuai dengan aktivasi dari clock tersebut, berikut ini merupakan rangkaian internal dari D flip flop:

Gambar 9 Rangkaian internal D flip flop

Gambar komponen serta tabel logika dari D flip - flop dapat diperhatikan pada gambar dibawah ini:

Gambar 10.Gambar komponen dari D flip flop

Gambar 11. Tabel logika dari D flip - flop dengan kondisi Active HIGH

Dapat dilihat bahwa nilai dari output Q sama dengan nilai input D. Namun, ini tidak berarti bahwa nilai dari keduanya sama pada setiap waktu, nilai ini akan sama hanya jika input data D berganti pada saat yang sama dengan aktivasi clock dari D flip flop ini.

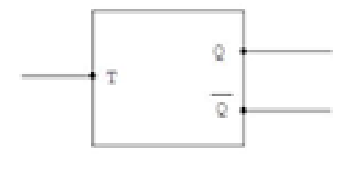

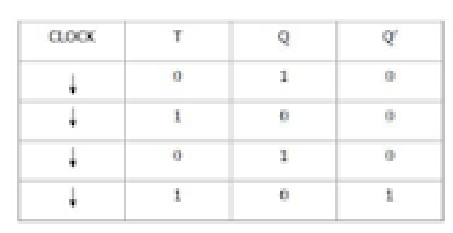

D, T flip-flop

T flip-flop merupakan modifikasi lanjutan dari J-K flip flop yang hanya memanfaatkan karakteristik toogle dari J-K flip flop saja, yang berarti T flip flop apabila diberi input 1 maka akan berada pada kondisi toogle, sementara apabila diberi input 0 maka outputnya akan tetap. Rangkaian internal dari T flip flop adalah sebagai berikut:

Untuk rangkaian internal dan tabel logika dari T flip flop adalah :Gambar 12. Simbol dari T flip - flop

Gambar 13. Tabel logika dari T flip flop

Apabila tabel logika dari T flip - flop diamati lebih lanjut dapat diambil kesimpulan jika input dari T flip flop tersebut adalah 0, maka nilai outputnya tidak akan berganti dari keadaan sebelumnya. Namun, jika inputnya adalah 0, nilai outputnya berganti sesuai dengan aktivasi clocknya (pada tabel tersebut adalah active LOW).

.jpeg)

Tidak ada komentar:

Posting Komentar