Laporan Akhir 1

1. Jurnal [Kembali]

Jurnal yang didapat dari praktikum dapat dilihat pada gambar dibawah ini:

2. Hardware [Kembali]

Hardware / alat serta bahan yang digunakan pada praktikum ini adalah sebagai berikut:

a. Jumper

c. Panel DL 2203C

d. Panel DL 2203S

Panel - panel diatas digabung menjadi sebuah modul yang disebut model D'Lorenzo

a. IC 74LS112 (J-K flip-flop IC)

b. Logic probe

c. Switch SPDT

d Power DC

Power DC yang digunakan pada percobaan kali ini adalah power supply DC

gambar 6. Power DC

3. Rangkaian [Kembali]

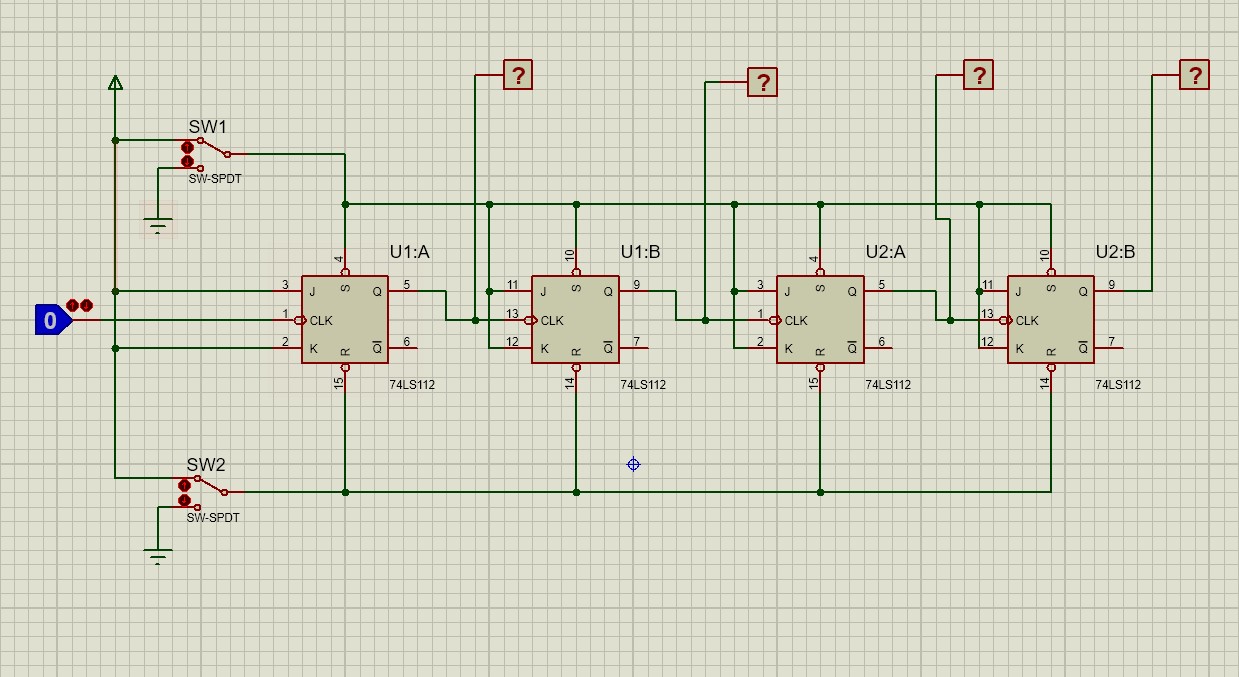

Gambar rangkaian simulasi akan dibagi menjadi 2 buah gambar, yakni ketika rangkaian tidak aktif, dan gambar ketika rangkaian aktif

a. Gambar rangkaian ketika berada pada keadaan tidak aktif

b. Gambar rangkaian ketika berada pada keadaan aktif

Gambar 8. Ragnakaian counter aktif

4. Prinsip Kerja [Kembali]

Prinsip kerja dari rangkaian ini bergantung terhadap prinsip kerja dari sebuah J-K flip - flop. Pada rangkaian diatas FF yang digunakan adalah berupa IC 74LS112 yang disusun secara seri sebanyak 4 buah FF, Pin dari J K dari masing - masing flip flop dihubungkan ke tegangan HIGH sehingga untuk setiap pergantian clock, kondisi output FF akan berada pada kondisi toogle (berganti), input clock dari FF pertama dihubungkan langsung dengan clock, sementara untuk input CLK dari masing - masing FF setelah dihubungkan dengan output dari FF sebelumnya, misal untuk input CLK FF ke3 dihubungkan ke output dari FF ke2 dan seterusnya.

Hal ini akan menyebabkan frekuensi dari setiap input CLK FF setelahnya dibagi menjadi 2 karena diketahui bahwa FF1 hanya berganti nilainya ketika memasuki 1 putaran clock (1 naik dan 1 turun). ketidaksinkronan inilah yang menyebabkan rangkaian diatas disebut sebagai rangkaian asynchronous.

Jadi. ketika input clock masuk dari FF 1, dan mengganti dari 1 ke 0, yang kemudian dijadikan input untuk pin CLK FF 2, output dari FF ke 2 akan berubah dari 0 ke 1, lalu pada pergantian 1 ke 0 selanjutnya akan terjadi hal yang sama, yakni output dari FF 2 berubah dari 1 ke 0, hal ini secara langsung mengaktifkan output FF ke 3 sehingga menajdi 1. Proses ini terus terjadi hingga batas maksimum angka. Batas maksimum perhitungan ini tergantung berapa banyak FF yang digunakan. dengan batas maks = 2^N - 1 dengan N adalah jumlah FF nya

Untuk melihat lebih jelas lagi berikut merupakan timing diagram dari rangkaian percobaan pertama:

Pengamatan lebih lanjut dari gambar dapat kita simpulkan bahwa masing - masing output (D0-D3) aktif dengan frekuensi lebih kecil 2 kali lipat dari output yang sebelumnya.

5. Video Praktikum [Kembali]

Untuk link video praktikumnnya adalah sebagai berikut:

6. Analsisis [Kembali]

Soal analisa:

a. Analisa output percobaan berdasarkan IC yang digunakan!

-> Pada percobaan ini menggunakan IC 74LS112 yakni IC J-K flip-flop untuk membuat rangkaian asynchronous counter, dan untuk output dari IC yang digunakan adalah masing - masing outputnya independen terhadap output-output sebelumnya. Untuk ouptut dari IC ini sendiri dapat bernilai 1 atau 0.

b. Analinsa sinyal output J-K flip-flop kedua dan ketiga!

-> Output pada J-K FF kedua akan aktif setiap terjadi dua putaran clock, yang berarti setiap dua putaran clock ouptu dari J-K FF kedua dapat berubah dari 1 ke 0 (atau sebaliknya). Sementara itu untuk output FF ke 3 akan berganti setiap 4 putaran clock. Terjadinya perbedaan tiitk pergantian nilai pada setiap FF menunjukkkan bahwa input clock masing-masing flip-flop tidak sinkron, maka dari itu disebut asychoronous

7. Link Download [Kembali]

Tidak ada komentar:

Posting Komentar